Imagínate un mundo donde la comunicación entre dispositivos es como un complejo baile, cada movimiento planeado y coordinado. En este escenario, el Registro de Dirección Base (BAR) en PCIe juega un papel clave. Si alguna vez te has preguntado qué significa o cómo afecta a tus dispositivos, estás en el lugar correcto. En esta exploración, desentrañaremos el enigma detrás del Base Address Register (BAR).

¿Qué es el Registro de Dirección Base (BAR) en PCIe?

El Registro de Dirección Base, o simplemente BAR, es un concepto crucial en el mundo de PCIe (Peripheral Component Interconnect Express). Cuando tus dispositivos electrónicos necesitan comunicarse, el BAR actúa como un «mapa» que indica la ubicación exacta de la información que deben intercambiar. Aquí es donde entran en juego los términos «pci bar» y «bar pci,» que se refieren específicamente a esta funcionalidad dentro del estándar PCIe.

Desglose Detallado del BAR:

Entendiendo el BAR: El BAR contiene información vital sobre las direcciones de memoria y puertos de entrada/salida (I/O) que los dispositivos utilizan para comunicarse. Esencialmente, es la clave que permite a los componentes electrónicos hablar el mismo idioma. La pregunta «address que es» se contesta en este contexto como la designación de espacios de memoria que los dispositivos utilizan para sus operaciones.

¿Cómo Funciona el BAR?: Cuando un dispositivo PCIe se conecta a la placa madre, utiliza su BAR para informar al sistema operativo sobre las áreas de memoria y puertos I/O que necesita. Este proceso facilita una comunicación sin fisuras entre los diferentes componentes de tu sistema y es esencial para entender «que es el pcie«.

¿Por qué el Registro de Dirección Base (BAR) Importa?

Imagina tu computadora como una ciudad interconectada, cada dispositivo es un edificio y el BAR es el plano maestro. Sin el BAR, los dispositivos no podrían encontrar sus direcciones y se perderían en el caos digital.

Optimizando el Rendimiento con el Base Address Register (BAR):

Cuando se trata de maximizar el rendimiento de tu sistema, entender y optimizar el BAR es clave. A través de configuraciones inteligentes, puedes mejorar la eficiencia de la comunicación entre tus dispositivos, permitiendo un flujo de datos más rápido y fluido. En este sentido, es importante considerar la optimización del «bar in pcie» para alcanzar un rendimiento óptimo.

El Registro de Dirección Base (BAR) en PCIe es como el GPS de tus dispositivos electrónicos. Permite una comunicación ordenada y eficiente, asegurando que cada componente sepa exactamente dónde encontrar la información que necesita.

Esperamos que esta exploración del Base Address Register haya aclarado tus dudas y te haya proporcionado una comprensión más profunda de la infraestructura vital que mantiene a tus dispositivos electrónicos conectados.

Recuerda, en el complejo baile de la tecnología, el BAR es el director de la orquesta, guiando a cada dispositivo para que toque la melodía de la eficiencia. ¡Sigue explorando el fascinante mundo de PCIe y mantén tu sistema en sintonía!

Soluciones

Punto de vista del kernel de Linux

Una buena forma de aprender algo es interactuando con ello, así que vamos a usar el kernel de Linux para eso, proporcionando una perspectiva práctica sobre el concepto de «pci bar«.

He aquí un ejemplo mínimo de PCI en un dispositivo emulado QEMU proporcionado por Cirosantilli: https://github.com/cirosantilli/linux-kernel-module-cheat/blob/366b1c1af269f56d6a7e6464f2862ba2bc368062/kernel_module/pci.c

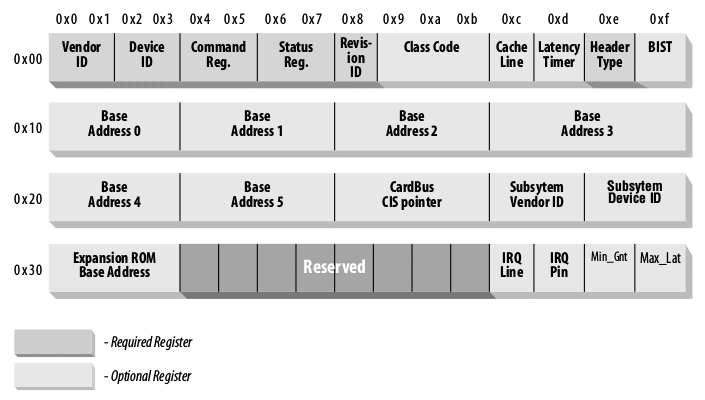

Los primeros 64 bytes de la configuración PCI están estandarizados como:

Imagen de LDD3.

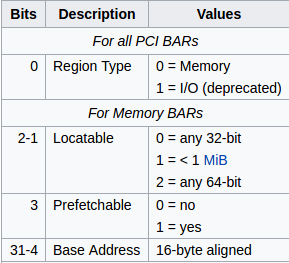

Así podemos ver que hay 6 BARs. A continuación, la página wiki muestra el contenido de cada BAR:

Sin embargo, el ancho de región requiere una escritura mágica: ¿Cómo se determina el tamaño de una PCI / PCIe BAR?

Esta memoria es configurada por el dispositivo PCI, y da información al kernel sobre la estructura del «bar pci«.

Cada BAR corresponde a un rango de direcciones que sirve como un canal de comunicación separado para el dispositivo PCI, una parte integral de la arquitectura «bar in pcie«.

La longitud de cada región es definida por el hardware, y comunicada al software a través de los registros de configuración, lo que responde a la pregunta «address que es» en el contexto de las configuraciones de hardware.

Además de la longitud, cada región tiene otras propiedades definidas por el hardware, en particular el tipo de memoria:

IORESOURCE_IO: debe accederse con inX y outX

IORESOURCE_MEM: se debe acceder con ioreadX y iowriteX

Varias funciones PCI del kernel de Linux toman el BAR como parámetro para identificar qué canal de comunicación se va a utilizar, por ejemplo:

mmio = pci_iomap(pdev, BAR, pci_resource_len(pdev, BAR)); pci_resource_flags(dev, BAR); pci_resource_start(pdev, BAR); pci_resource_end(pdev, BAR);

Mirando en el código fuente del dispositivo QEMU, vemos que los dispositivos QEMU registran esas regiones con:

memory_region_init_io(&edu->mmio, OBJECT(edu), &edu_mmio_ops, edu,

"edu-mmio", 1 << 20);

pci_register_bar(pdev, 0, PCI_BASE_ADDRESS_SPACE_MEMORY, &edu->mmio);

y queda claro que las propiedades de la BAR están definidas por hardware, por ejemplo, la BAR número 0, tiene tipo memoria PCI_BASE_ADDRESS_SPACE_MEMORY, y la región de memoria es de 1MiB de longitud 1 << 20, lo que es crucial para entender «que es el pcie» y su funcionamiento.